Senior Chip Design Engineer at

NXP Semiconductor

NXP designs purpose-built, rigorously tested technologies that enable devices to sense, think, connect and act intelligently to improve people's daily lives.

Backend Physical Design Team

My Role:

Skills:

Soft Skills: I thrive in an interdisciplinary environment, learning and collaborating with corss-functional teams from India, Austin and Munich. I also mentored two freshers.

Field: Synthesis and Logical Equivalence Check

Tool Skills: Synopsys design compiler and Cadence Conformal

Field: Power Specifications and Optimizations

Tool Skills: Cadence Vclp and Synopsys Redhawk

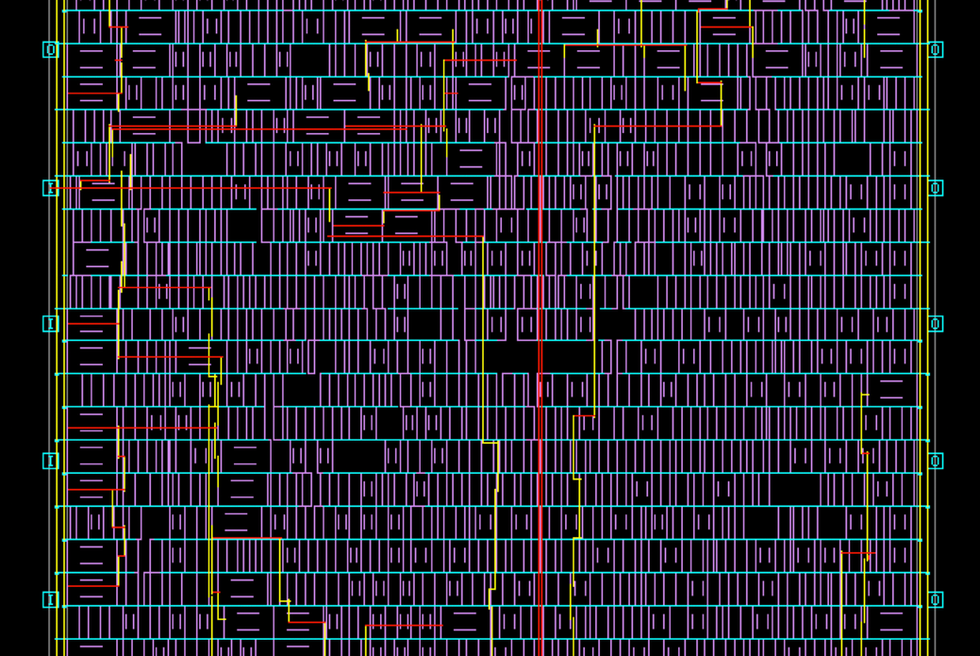

Field: Placement, CTS and Routing

Tool Skills: Synopsys IC Compiler II, ICV for design rule checks

I work on vision and radar based ADAS automotive chips with 16 and 5 nanometer finFET technology. I have ownership for IPs like Dual data rate (DDR) and High Security Engine (HSE encrypted IP) which work on system clock frequency of 400Mhz with gate count of 9.5 lacs and a high utilization of 74.4%. I perform the following activities as a Backend Physical Designer:

The application/architecture of the chip is coded in Verilog. During synthesis, the code is converted to simple gate-level design with as much optimization as possible to reduce chip size keeping the design intent intact.

Well connected power grid is designed for the chip in modes like on/of/standby/low-power. Modifications are made such that there are no hot spots or power drop across the chip.

The components/gates on the chip are placed such that there is minimal routing resources used and the applications are executed well within the clock cycle on which the chip works without any crosstalk noise or glitch disturbance. I worked on a 400Mhz frequency block with an oscillator that produced upto 1.3Ghz clock frequency.